4.2 Assembly Language

AS Level · 3 questions found

What this topic covers

Section titled “What this topic covers”- Relationship between assembly language and machine code

- Two-pass assembler: stages and applying to a program

- Trace a simple assembly language program

- Instruction groups: data movement, I/O, arithmetic, jump, compare

- Addressing modes: immediate, direct, indirect, indexed, relative

- Key instructions: LDM, LDD, LDI, LDX, STO, ADD, SUB, JMP, CMP, JPE, JPN, IN, OUT, END

Past paper questions

Section titled “Past paper questions” Q4

4

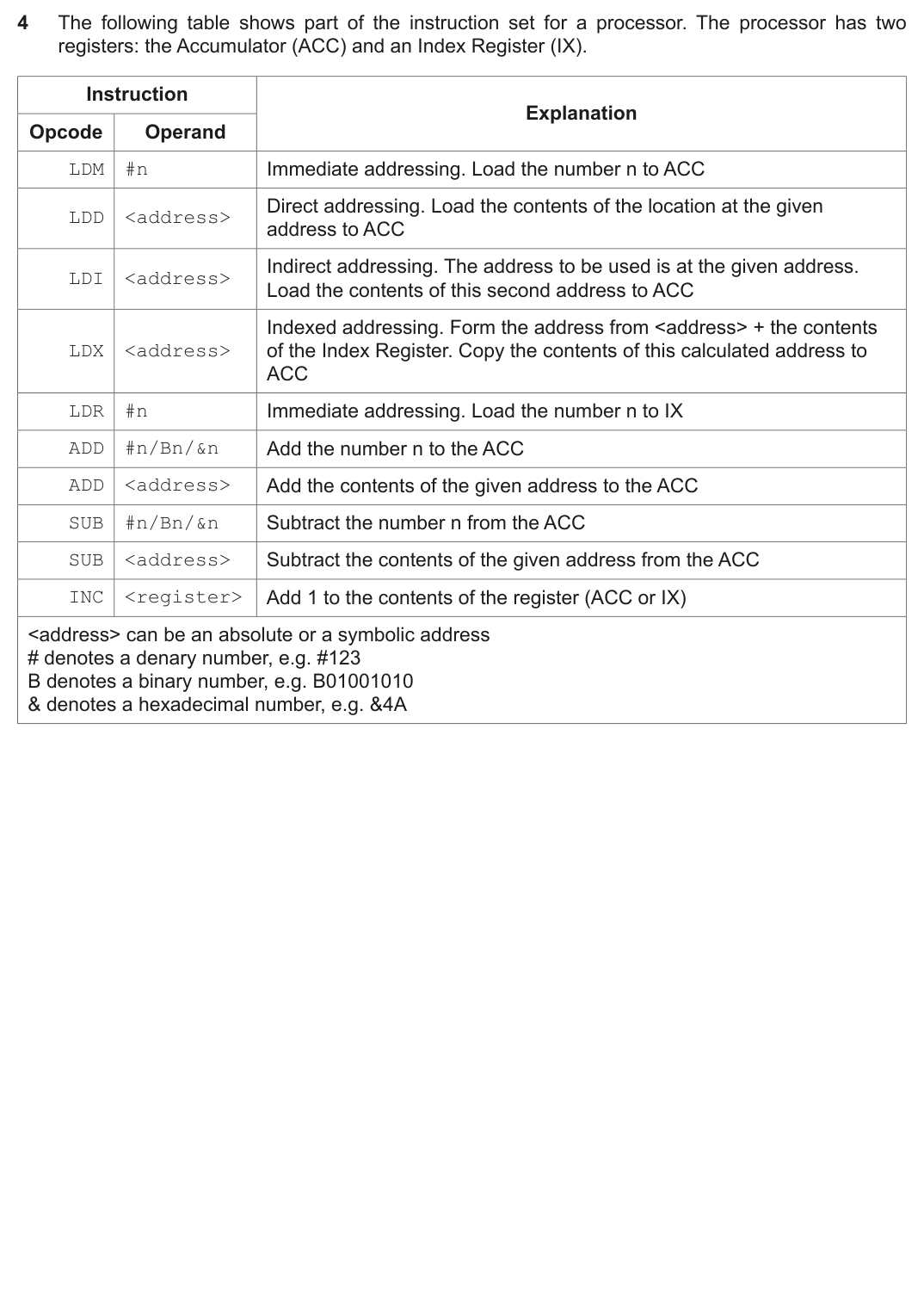

The following table shows part of the instruction set for a processor. The processor has two

registers: the Accumulator (ACC) and an Index Register (IX).

Instruction

Explanation

Opcode

Operand

LDM

#n

Immediate addressing. Load the number n to ACC

LDD

<address>

Direct addressing. Load the contents of the location at the given

address to ACC

LDI

<address>

Indirect addressing. The address to be used is at the given address.

Load the contents of this second address to ACC

LDX

<address>

Indexed addressing. Form the address from <address> + the contents

of the Index Register. Copy the contents of this calculated address to

ACC

LDR

#n

Immediate addressing. Load the number n to IX

ADD

#n/Bn/&n

Add the number n to the ACC

ADD

<address>

Add the contents of the given address to the ACC

SUB

#n/Bn/&n

Subtract the number n from the ACC

SUB

<address>

Subtract the contents of the given address from the ACC

INC

<register>

Add 1 to the contents of the register (ACC or IX)

<address> can be an absolute or a symbolic address

# denotes a denary number, e.g. #123

B denotes a binary number, e.g. B01001010

& denotes a hexadecimal number, e.g. &4A

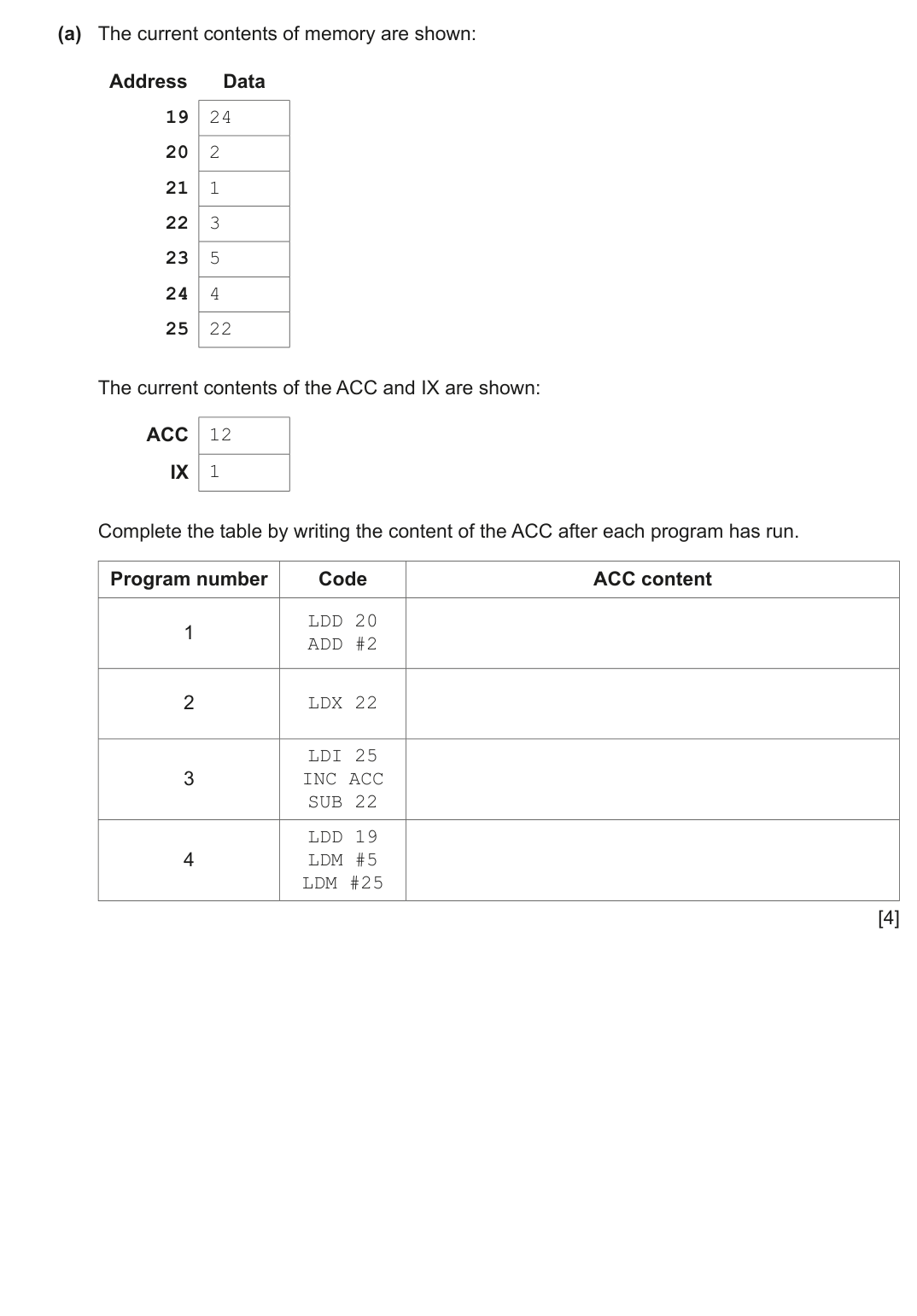

(a) The current contents of memory are shown:

Address

Data

19

24

20

2

21

1

22

3

23

5

24

4

25

22

The current contents of the ACC and IX are shown:

ACC

12

IX

1

Complete the table by writing the content of the ACC after each program has run.

Program number

Code

ACC content

1

LDD 20

ADD #2

2

LDX 22

3

LDI 25

INC ACC

SUB 22

4

LDD 19

LDM #5

LDM #25

[4]

(b) The processor includes these bit manipulation instructions:

Instruction

Explanation

Opcode

Operand

AND

#n/Bn/&n

Bitwise AND operation of the contents of ACC with the operand

AND

<address>

Bitwise AND operation of the contents of ACC with the contents of

<address>

XOR

#n/Bn/&n

Bitwise XOR operation of the contents of ACC with the operand

XOR

<address>

Bitwise XOR operation of the contents of ACC with the contents of

<address>

OR

#n/Bn/&n

Bitwise OR operation of the contents of ACC with the operand

OR

<address>

Bitwise OR operation of the contents of ACC with the contents of

<address>

<address> can be an absolute or a symbolic address

# denotes a denary number, e.g. #123

B denotes a binary number, e.g. B01001010

& denotes a hexadecimal number, e.g. &4A

The current contents of memory are shown:

Address

Data

30

01110101

31

11111111

32

00000000

33

11001100

34

10101010

The current content of the ACC is shown:

1

0

0

1

1

0

1

0

Complete the table by writing the content of the ACC after each program has run.

The binary number 10011010 is reloaded into the ACC before each program is run.

Program number

Code

ACC content

1

AND 31

2

XOR B01001111

3

OR #30

[3]

Show mark scheme

4(a) [4 marks]

1 mark

for each correct answer:

Program

Code

ACC

Number

Content

LDD 20

1

4

ADD #2

LDX 22

2

5

LDI 25

3

1

INC ACC

SUB 22

LDD 19

4

25

LDM #5

LDM #25

for each correct answer:

Program

Code

ACC

Number

Content

LDD 20

1

4

ADD #2

LDX 22

2

5

LDI 25

3

1

INC ACC

SUB 22

LDD 19

4

25

LDM #5

LDM #25

4(b) [3 marks]

1 mark

for each correct answer:

Program

Code

ACC Content

Number

AND 31

1

1001 1010

XOR B01001111

2

1101 0101

OR #30

3

1001 1110

for each correct answer:

Program

Code

ACC Content

Number

AND 31

1

1001 1010

XOR B01001111

2

1101 0101

OR #30

3

1001 1110

Q5

5

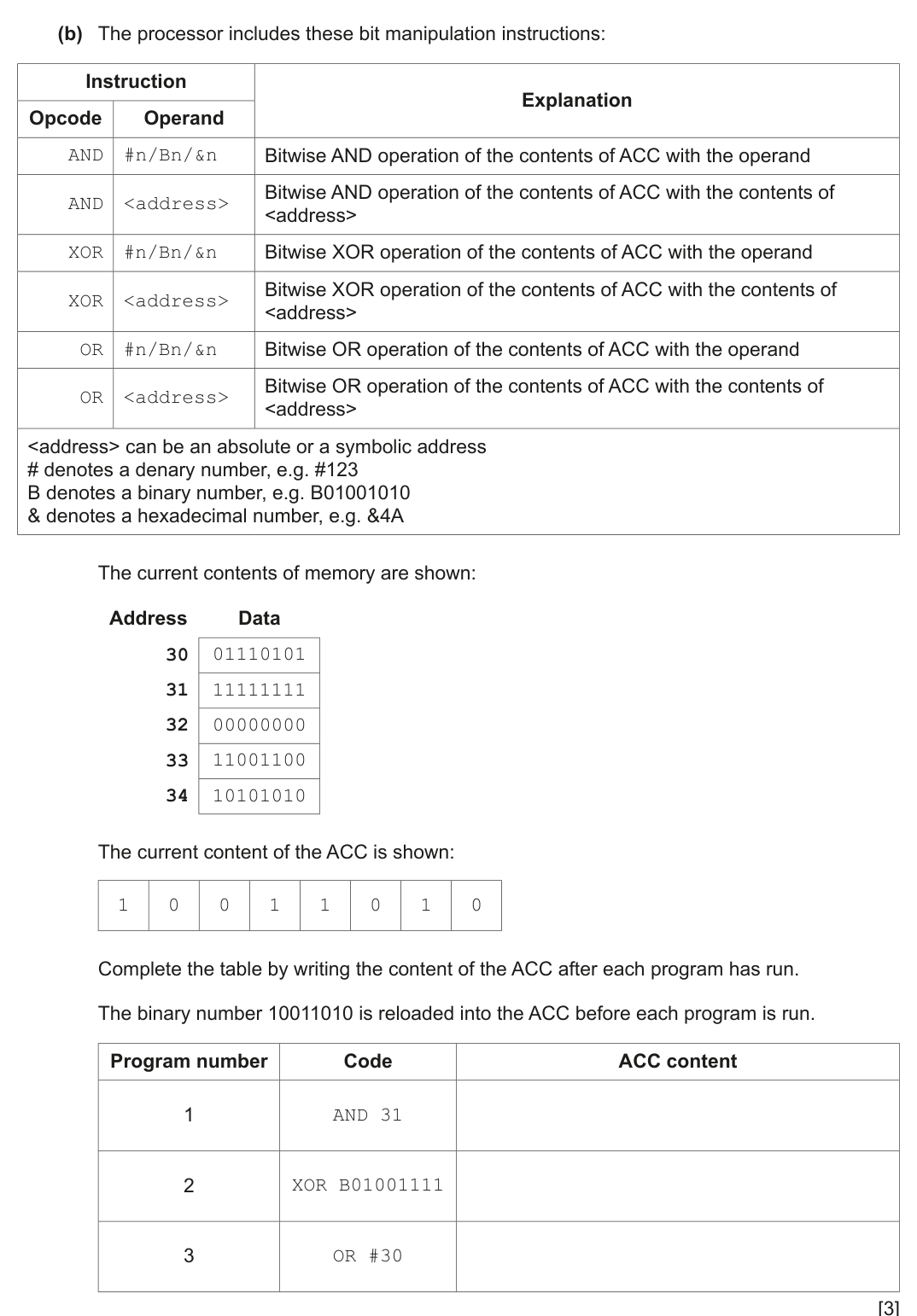

The following table shows part of the instruction set for a processor. The processor has two

registers: the Accumulator (ACC) and an Index Register (IX).

Instruction

Explanation

Opcode

Operand

LDM

#n

Immediate addressing. Load the number n to ACC

LDD

<address>

Direct addressing. Load the contents of the location at the given

address to ACC

LDI

<address>

Indirect addressing. The address to be used is at the given address.

Load the contents of this second address to ACC

LDX

<address>

Indexed addressing. Form the address from <address> + the contents

of the index register. Copy the contents of this calculated address to

ACC

LDR

#n

Immediate addressing. Load the number n to IX

ADD

#n/Bn/&n

Add the number n to the ACC

ADD

<address>

Add the contents of the given address to the ACC

SUB

#n/Bn/&n

Subtract the number n from the ACC

SUB

<address>

Subtract the contents of the given address from the ACC

INC

<register>

Add 1 to the contents of the register (ACC or IX)

<address> can be an absolute or a symbolic address

# denotes a denary number, e.g. #123

B denotes a binary number, e.g. B01001010

& denotes a hexadecimal number, e.g. &4A

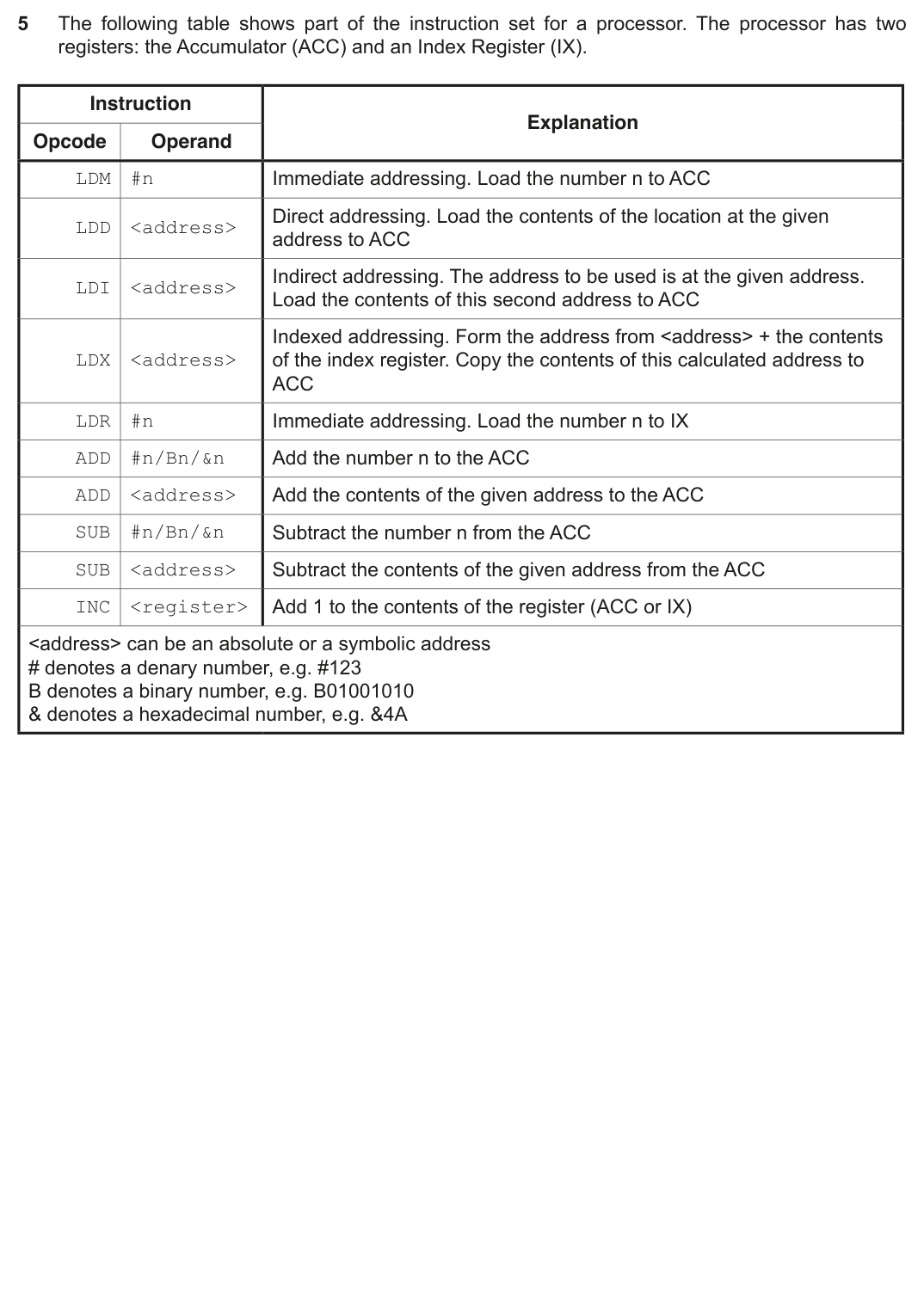

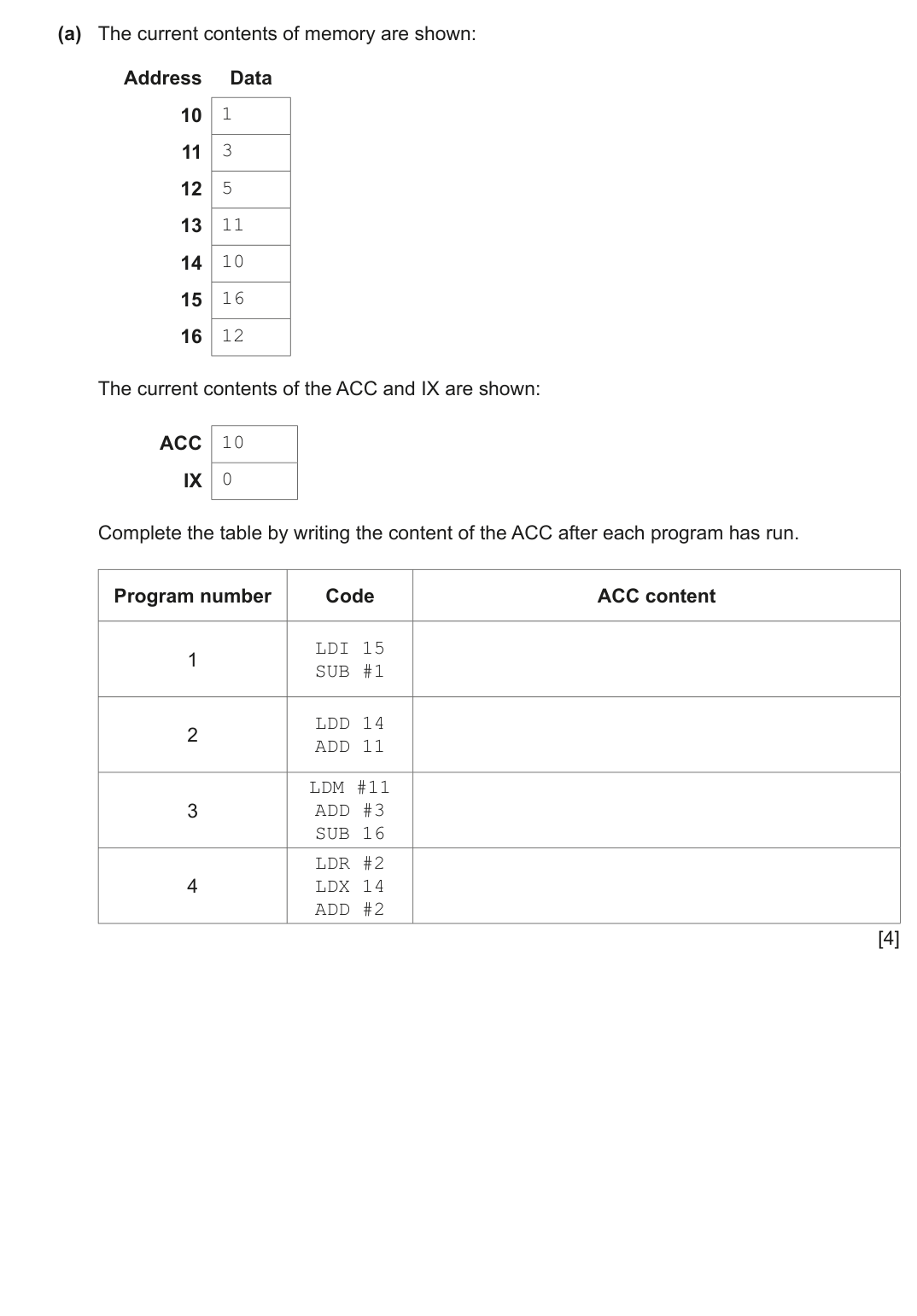

(a) The current contents of memory are shown:

Address

Data

10

1

11

3

12

5

13

11

14

10

15

16

16

12

The current contents of the ACC and IX are shown:

ACC

10

IX

0

Complete the table by writing the content of the ACC after each program has run.

Program number

Code

ACC content

1

LDI 15

SUB #1

2

LDD 14

ADD 11

3

LDM #11

ADD #3

SUB 16

4

LDR #2

LDX 14

ADD #2

[4]

(b) The processor includes these bit manipulation instructions:

Instruction

Explanation

Opcode

Operand

AND

#n/Bn/&n

Bitwise AND operation of the contents of ACC with the operand

AND

<address>

Bitwise AND operation of the contents of ACC with the contents of

<address>

XOR

#n/Bn/&n

Bitwise XOR operation of the contents of ACC with the operand

XOR

<address>

Bitwise XOR operation of the contents of ACC with the contents of

<address>

OR

#n/Bn/&n

Bitwise OR operation of the contents of ACC with the operand

OR

<address>

Bitwise OR operation of the contents of ACC with the contents of

<address>

<address> can be an absolute or a symbolic address

# denotes a denary number, e.g. #123

B denotes a binary number, e.g. B01001010

& denotes a hexadecimal number, e.g. &4A

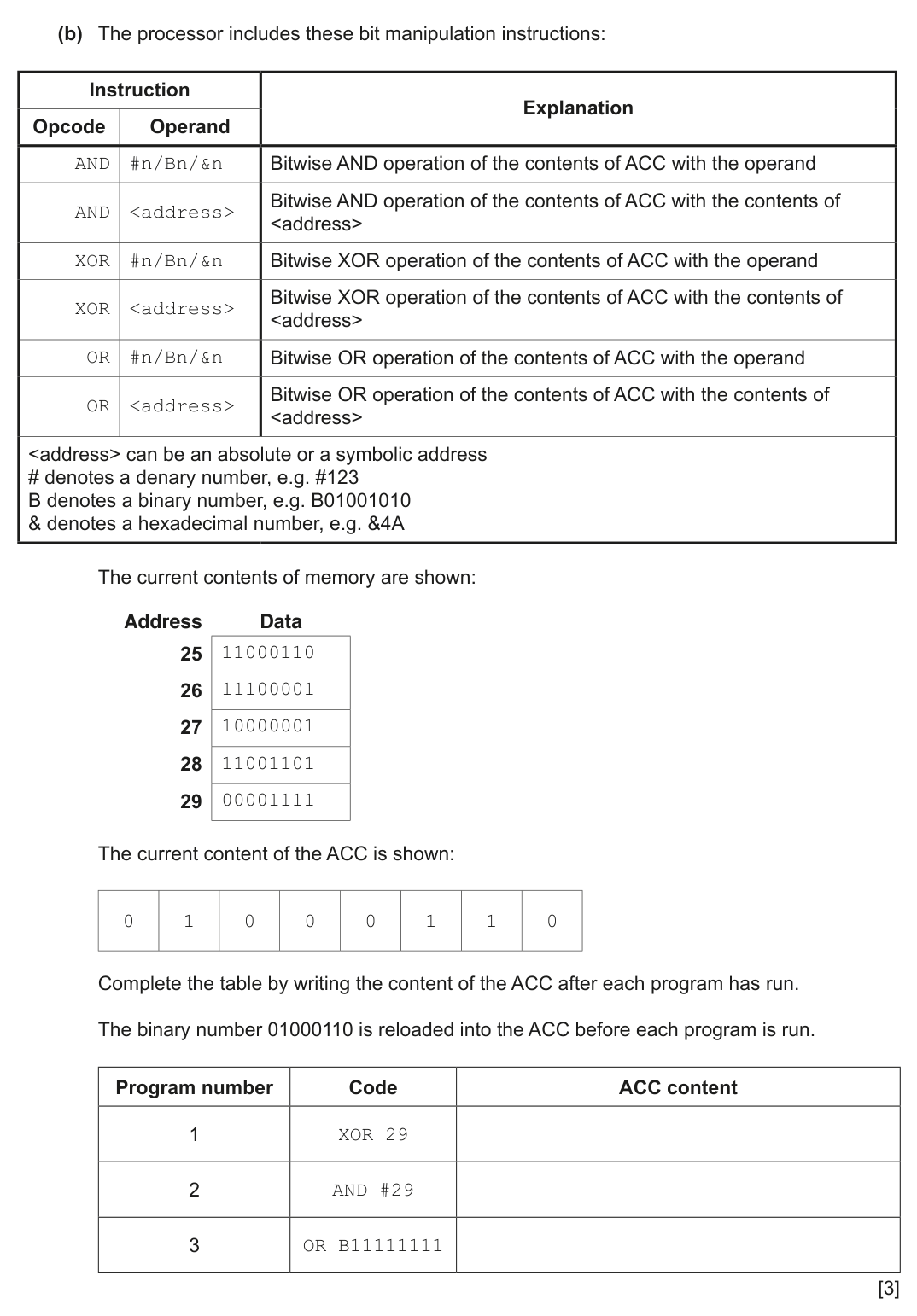

The current contents of memory are shown:

Address

Data

25

11000110

26

11100001

27

10000001

28

11001101

29

00001111

The current content of the ACC is shown:

0

1

0

0

0

1

1

0

Complete the table by writing the content of the ACC after each program has run.

The binary number 01000110 is reloaded into the ACC before each program is run.

Program number

Code

ACC content

1

XOR 29

2

AND #29

3

OR B11111111

[3]

Show mark scheme

5(a) [4 marks]

1 mark

for each correct answer:

Program

Code

ACC Content

Number

1

LDI 15

11

SUB #1

2

LDD 14

13

ADD 11

2

3

LDM #11

ADD #3

SUB 16

4

LDR #2

14

LDX 14

ADD #2

for each correct answer:

Program

Code

ACC Content

Number

1

LDI 15

11

SUB #1

2

LDD 14

13

ADD 11

2

3

LDM #11

ADD #3

SUB 16

4

LDR #2

14

LDX 14

ADD #2

5(b) [3 marks]

1 mark for

each correct answer:

Program

Code

ACC Content

Number

1

XOR 29

0100 1001

2

AND #29

0000 0100

3

OR B11111111

1111 1111

each correct answer:

Program

Code

ACC Content

Number

1

XOR 29

0100 1001

2

AND #29

0000 0100

3

OR B11111111

1111 1111

Q3

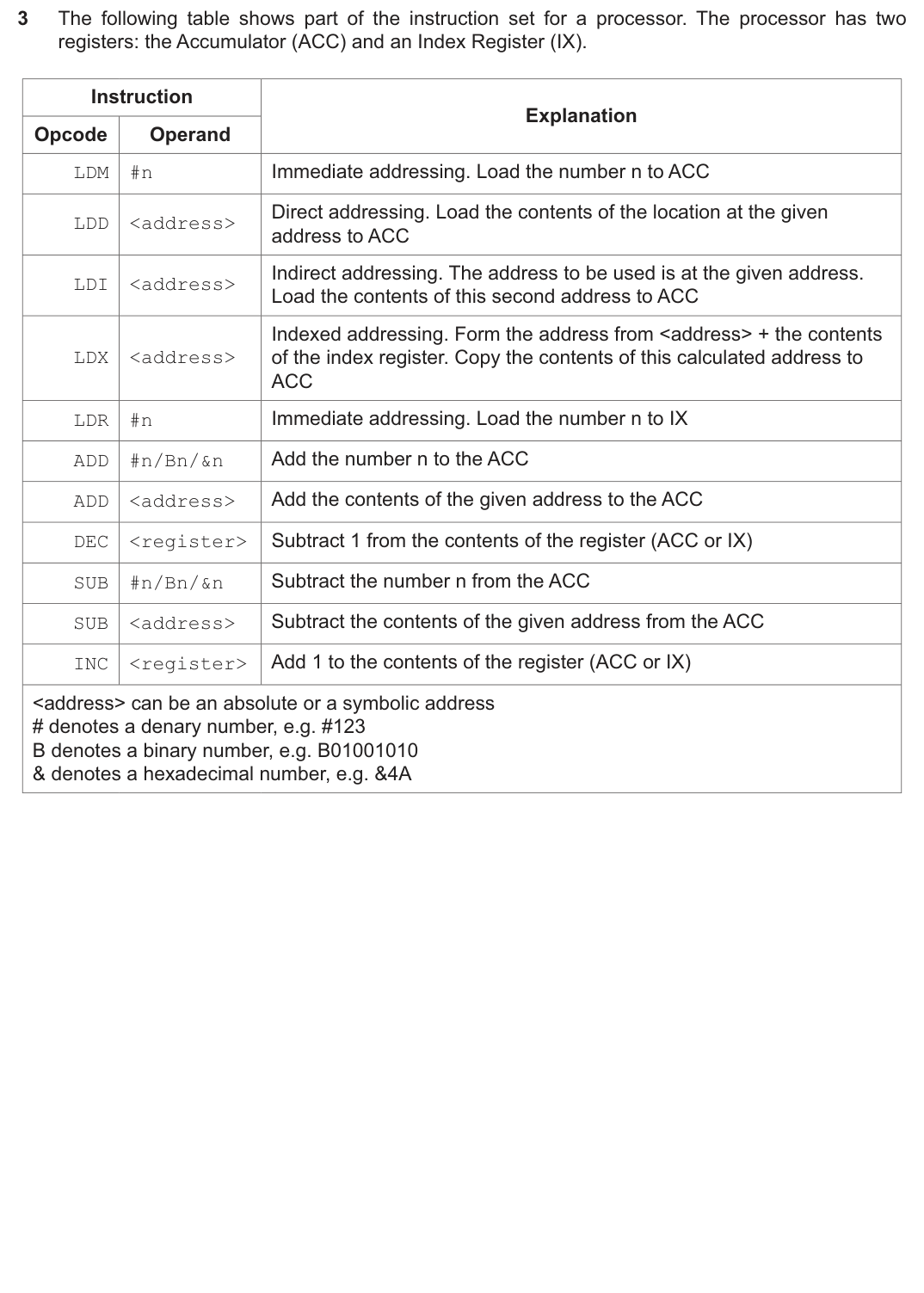

3

The following table shows part of the instruction set for a processor. The processor has two

registers: the Accumulator (ACC) and an Index Register (IX).

Instruction

Explanation

Opcode

Operand

LDM

#n

Immediate addressing. Load the number n to ACC

LDD

<address>

Direct addressing. Load the contents of the location at the given

address to ACC

LDI

<address>

Indirect addressing. The address to be used is at the given address.

Load the contents of this second address to ACC

LDX

<address>

Indexed addressing. Form the address from <address> + the contents

of the index register. Copy the contents of this calculated address to

ACC

LDR

#n

Immediate addressing. Load the number n to IX

ADD

#n/Bn/&n

Add the number n to the ACC

ADD

<address>

Add the contents of the given address to the ACC

DEC

<register>

Subtract 1 from the contents of the register (ACC or IX)

SUB

#n/Bn/&n

Subtract the number n from the ACC

SUB

<address>

Subtract the contents of the given address from the ACC

INC

<register>

Add 1 to the contents of the register (ACC or IX)

<address> can be an absolute or a symbolic address

# denotes a denary number, e.g. #123

B denotes a binary number, e.g. B01001010

& denotes a hexadecimal number, e.g. &4A

(a) The current contents of memory are shown:

Address

Data

48

51

49

6

50

48

51

50

52

49

53

50

54

6

The current contents of the ACC and IX are shown:

ACC

2

IX

50

Complete the table by writing the content of the ACC after each program has run.

Program number

Code

ACC content

1

LDM #50

INC ACC

SUB #1

2

LDI 51

ADD 52

3

LDR #2

LDX 50

DEC ACC

4

LDD 52

SUB 54

INC ACC

[4]

,

,

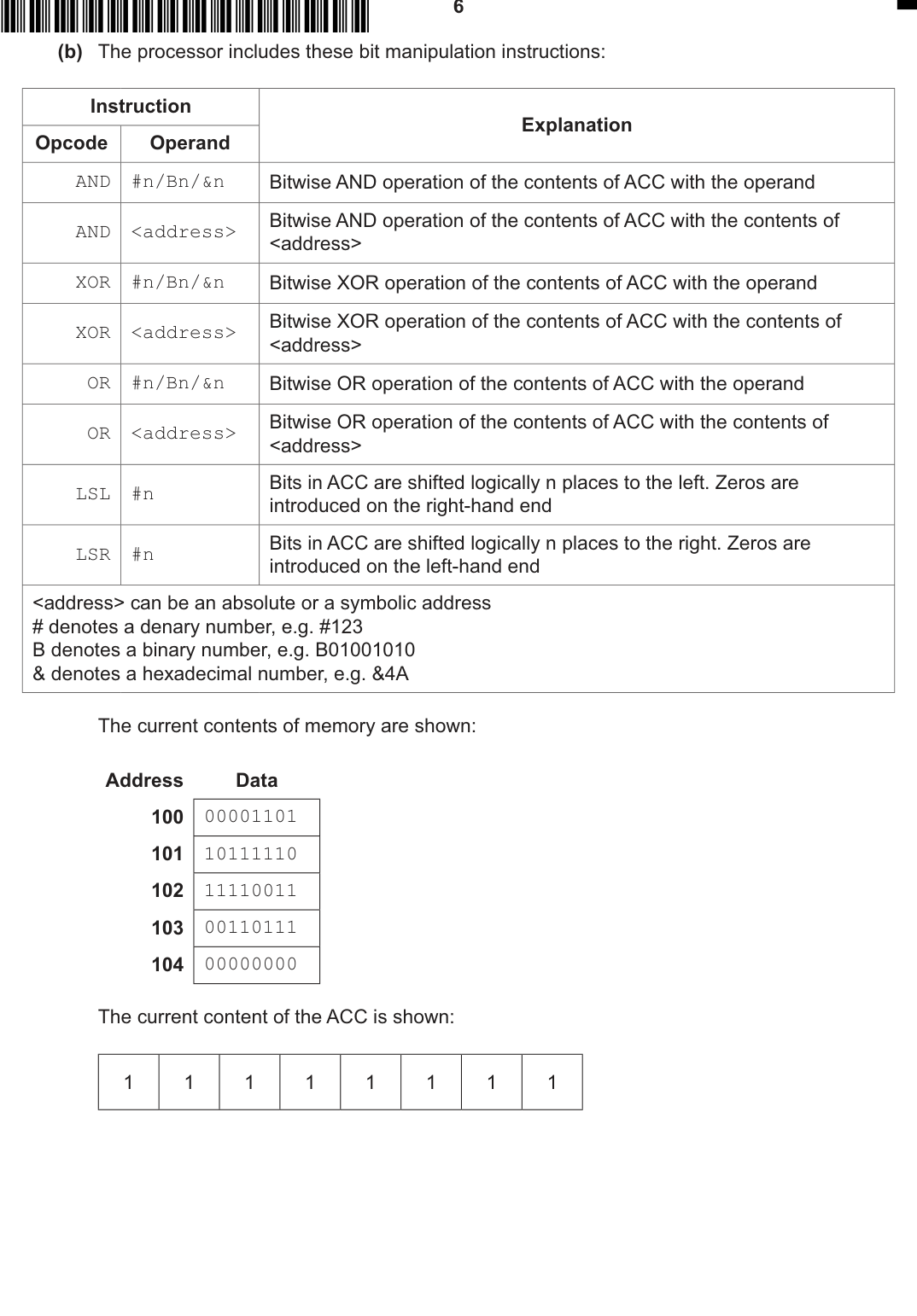

(b) The processor includes these bit manipulation instructions:

Instruction

Explanation

Opcode

Operand

AND

#n/Bn/&n

Bitwise AND operation of the contents of ACC with the operand

AND

<address>

Bitwise AND operation of the contents of ACC with the contents of

<address>

XOR

#n/Bn/&n

Bitwise XOR operation of the contents of ACC with the operand

XOR

<address>

Bitwise XOR operation of the contents of ACC with the contents of

<address>

OR

#n/Bn/&n

Bitwise OR operation of the contents of ACC with the operand

OR

<address>

Bitwise OR operation of the contents of ACC with the contents of

<address>

LSL

#n

Bits in ACC are shifted logically n places to the left. Zeros are

introduced on the right-hand end

LSR

#n

Bits in ACC are shifted logically n places to the right. Zeros are

introduced on the left-hand end

<address> can be an absolute or a symbolic address

# denotes a denary number, e.g. #123

B denotes a binary number, e.g. B01001010

& denotes a hexadecimal number, e.g. &4A

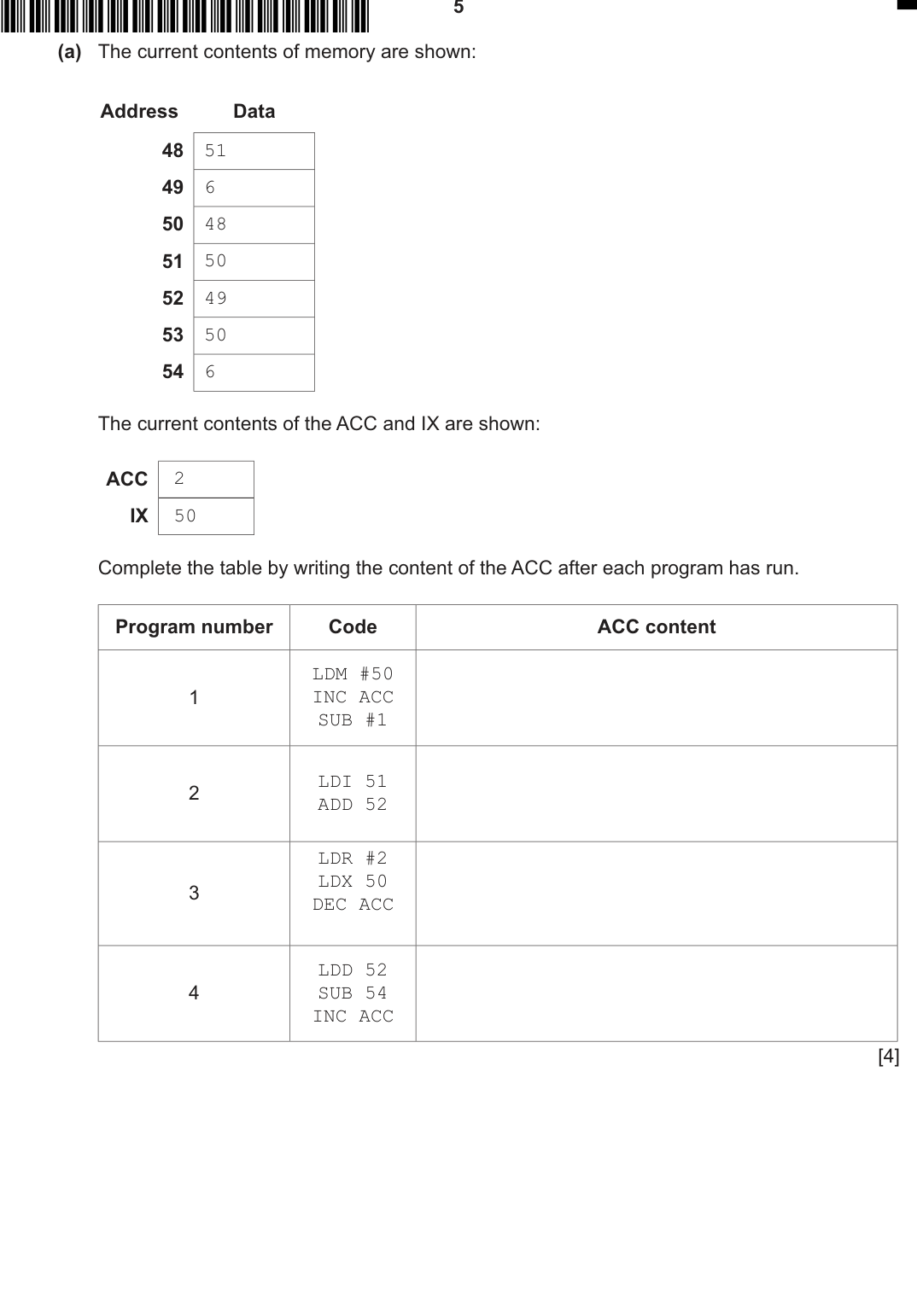

The current contents of memory are shown:

Address

Data

100

00001101

101

10111110

102

11110011

103

00110111

104

00000000

The current content of the ACC is shown:

1

1

1

1

1

1

1

1

,

,

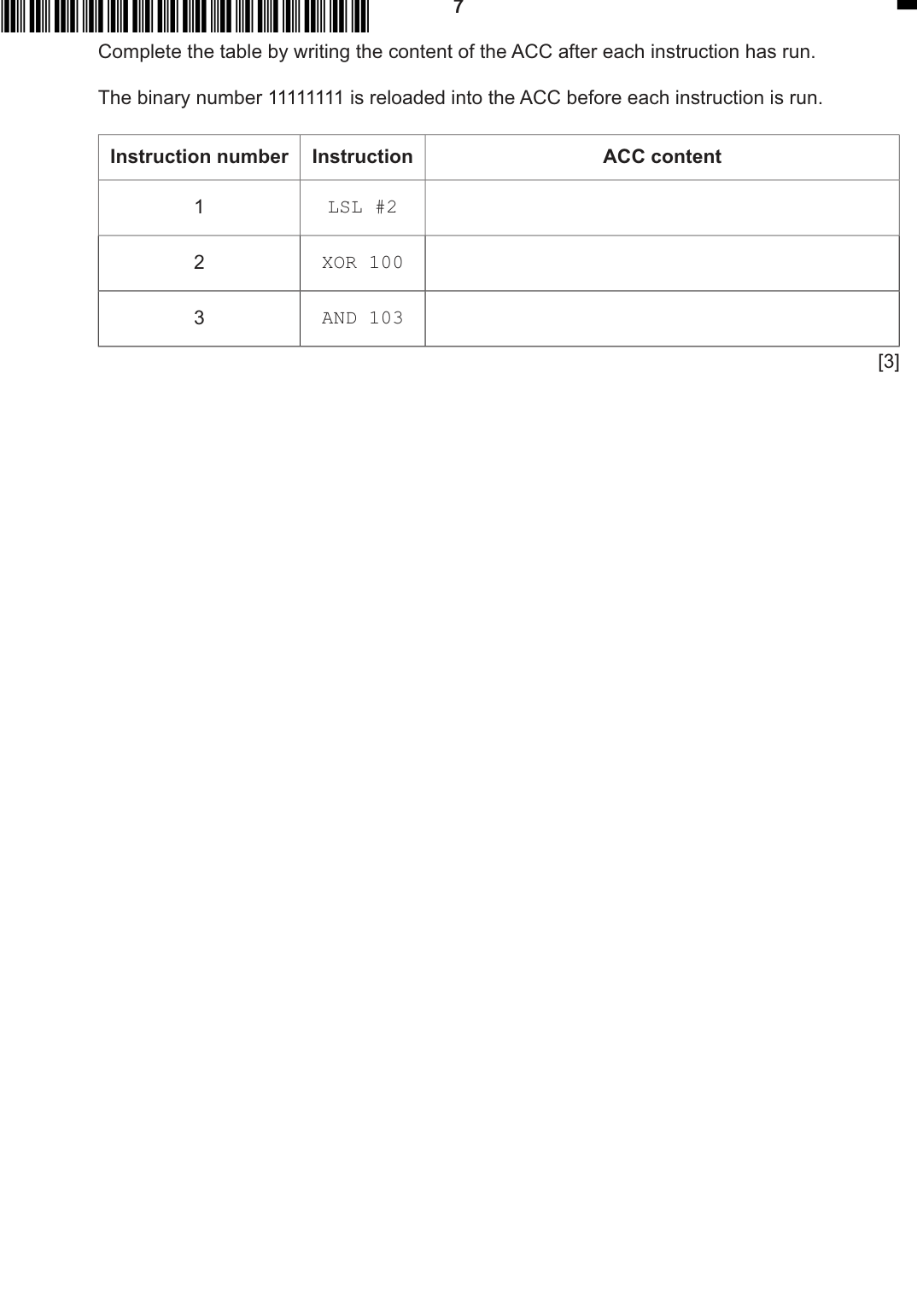

Complete the table by writing the content of the ACC after each instruction has run.

The binary number 11111111 is reloaded into the ACC before each instruction is run.

Instruction number

Instruction

ACC content

1

LSL #2

2

XOR 100

3

AND 103

[3]

,

,

,

,

Show mark scheme

3(a) [4 marks]

1 mark

for each correct answer:

Program

Code

ACC

Number

Content

LDM #50

1

50

INC ACC

SUB #1

LDI 51

2

97

ADD 52

LDR #2

3

48

LDX 50

DEC ACC

LDD 52

4

44

SUB 54

INC ACC

for each correct answer:

Program

Code

ACC

Number

Content

LDM #50

1

50

INC ACC

SUB #1

LDI 51

2

97

ADD 52

LDR #2

3

48

LDX 50

DEC ACC

LDD 52

4

44

SUB 54

INC ACC

3(b) [3 marks]

1 mark

for each correct answer:

Instruction

Instruction

ACC Content

Number

LSL #2

1

1111 1100

XOR 100

2

1111 0010

AND 103

3

0011 0111

for each correct answer:

Instruction

Instruction

ACC Content

Number

LSL #2

1

1111 1100

XOR 100

2

1111 0010

AND 103

3

0011 0111